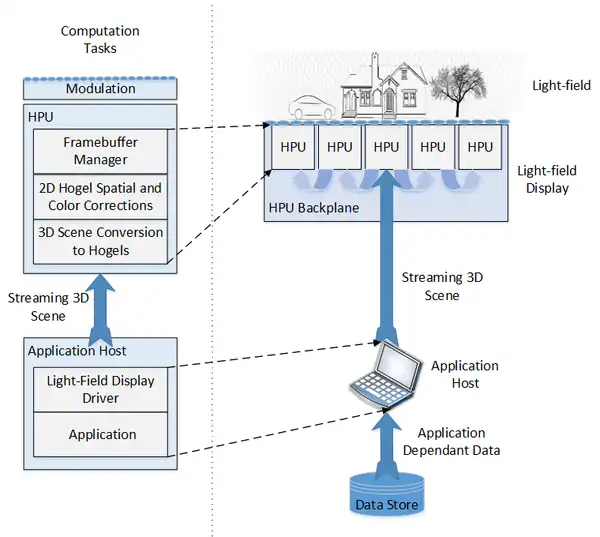

The Hogel processing unit (HPU) is a computation for rendering hogels.[1]

HPU parallelism Since many (possibly hundreds) HPUs would be required to drive a single light-field display, it is important that the HPU be an independent processor, requiring minimal support logic and interconnect. The HPU interconnect framework should provide scene, command and sync buffering and relay throughout the topology. Ideally, neither the host system nor the individual HPUs would have knowledge of the interconnect topology or even the depth and breadth of the system.

Hogel parallelism (multivew point rendering) A critical component of the HPU is the rendering of multiple viewpoints (hogels) in parallel per rendering pass of the geometry to take advantage of vertex and texture cache coherency.

Further reading

- Klug, M., Burnett, T., Fancello, A., Heath, A., Gardner, K., O'Connell, S., Newswanger, C. (2013). "A Scalable, Collaborative, Interactive Light-field Display System", SID Symposium Digest of Technical Papers

References

- ↑ Lucente, Mark (September 1994). "Diffraction-Specific Fringe Computation for Electro-Holography". MIT Dept. of Electrical Engineering and Computer Science. See, for example, page 55 in "Chapter 4: Diffraction-Specific Computation", or the "Glossary of Terms and Abbreviations" in Appendix A on page 151.