Serial general purpose input/output (SGPIO) is a four-signal (or four-wire) bus used between a host bus adapter (HBA) and a backplane. Of the four signals, three are driven by the HBA and one by the backplane. Typically, the HBA is a storage controller located inside a server, desktop, rack or workstation computer that interfaces with hard disk drives or solid state drives to store and retrieve data. It is considered an extension of the general-purpose input/output (GPIO) concept.

The SGPIO specification is maintained by the Small Form Factor Committee in the SFF-8485 standard. The International Blinking Pattern Interpretation indicates how SGPIO signals are interpreted into blinking light-emitting diodes (LEDs) on disk arrays and storage back-planes.

History

SGPIO was developed as an engineering collaboration between American Megatrends Inc, at the time makers of back-planes, and LSI-Logic in 2004. SGPIO was later published by the SFF committee as specification SFF-8485.

Host bus adapters

Typical host bus adapter with two 4× iPass connectors |

The SGPIO signal consists of 4 electrical signals; it typically originates from a host bus adapter (HBA). iPass connectors (Usually SFF-8087 or SFF-8484) carry both SAS/SATA electrical connections between the HBA and the hard drives as well as the 4 SGPIO signals.

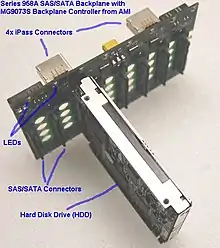

Backplanes with SGPIO bus interface

A backplane is a circuit board with connectors and power circuitry into which hard drives are attached; they can have multiple slots, each of which can be populated with a hard drive. Typically the back-plane is equipped with LEDs which by their color and activity, indicate the slot's status; typically, a slot's LED will emit a particular color or blink pattern to indicate its current status.

SGPIO interpretation and LED blinking patterns

Although many hardware vendors define their own proprietary LED blinking pattern, the common standard for SGPIO interpretation and LED blinking pattern can be found in the IBPI specification.

On back-planes, vendors use typically 2 or 3 LEDs per slot – in both implementations a green LED indicates presence and/or activity – for back-planes with 2 LEDs per slot, the second LED indicates Status whereas in back-planes with 3 LEDs the second and third indicate Locate and Fail.

Electrical characteristics of the SGPIO bus

The SGPIO bus consists of 4 signal lines and originates at the HBA, referred to as the initiator and ends at a back-plane, referred to as the target. If a back-plane (or target) is not present the HBA may still drive the bus without any harm to the system; if one does exist, it can communicate back to the HBA using the 4th wire.

The SGPIO bus is an open collector bus with 2.0 kΩ pull-up resistors located at the HBA and the back-plane - as on any open collector bus information is transferred by devices on the bus pulling the lines to ground (GND) using an open collector transistor or open drain FET.

Signal lines of the SGPIO bus

SClock

The SGPIO bus has a dedicated clock line driven by the initiator (its maximum clock rate is 100 kHz), although many implementations use slower ones (typically 48 kHz).

SLoad

This line is synchronous to the clock and is used to indicate the start of a new frame of data; a new SGPIO frame is indicated by SLoad being high at a rising edge of a clock after having been low for at least 5 clock cycles. The following 4 falling clock edges after a start condition is used to carry a 4-bit value from the HBA to the back-plane; the definition of this value is proprietary and varies between system vendors.

SDataOut

This line carries 3 bits of data from the HBA to the backplane: the first bit typically carries activity; the second bit carries locate; and the third bit carries fail. A low value for the first bit indicates no activity and a high value indicates activity.

SDataIn

This line is used by the back-plane and indicates some condition on the back-plane back to the HBA. The first bit being high commonly indicates the presence of a drive. The two following bits are typically unused, and driven low. Because this line would be high for all 3 bits when no backplane is connected, an HBA can detect the presence of a back-plane by the second or third bit of the SDataIn being driven low.

The SDataIn and SdataOut then repeats with 3 clocks per drive until the last drive is reached, and the cycle starts over again.

SGPIO implementation

There are varieties in how the SGPIO bus is implemented between vendors of HBAs and storage controllers - some vendors will send a continuous stream of data which is advantageous to quickly update the LEDs on a backplane after cables are removed and re-inserted, while others send data only when there is a need to update the LED pattern.

Adoption of the SGPIO specification

SGPIO and the SGPIO spec. is generally adopted and implemented in products from most major HBA and storage controller vendors such as LSI, Intel, Adaptec, Nvidia, Broadcom, Marvell Technology Group and PMC-Sierra. Most products shipping with support for SAS and SATA drives support this standard.

SGPIO timeout conditions

The SGPIO spec calls for the target to turn off all indicators when SClock, SLoad and SDataOut have been high for 64 ms; in practice this is not consistently followed by all vendors. Also, in some vendors' implementations the clock may be halted sporadically or stopped during or between cycles. Another — rather impractical — variation between vendors is the state in which the clock is left after a cycle.

Backplane Implementations of the SGPIO bus

The idea behind this specification was to be able to use low cost CPLDs or microcontrollers on a back-plane to drive LEDs; in practice, it has been found that there are variations in timing and interpretations of the bits between vendors, thus a simple CPLD would only work for a specific implementation thoroughly tested with one product from one vendor. A microcontroller is more applicable for this purpose, although the 4-bit SGPIO interface custom bus is not implemented on them - sampling of the 4-bit lines using GPIOs 100 kHz bit operations is too slow for many low-cost microcontrollers to handle whilst handling LED and other functions simultaneously. The length of the bit stream varies between HBA or storage controller; some vendors will stop the bit-stream when reaching the desired drive, while others will clock it all the way through. Some SAS-expander's bit streams may be as long as 108 (36×3) bits.

The safest implementation which ensures compatibility between all HBA and storage controller vendors is to use an ASIC, specifically, a combination of a microcontroller core with a hardware SGPIO interface; this concept was patented in 2006 by AMI and implemented in a series of backplane controller chips named the MG9071, MG9072, MG9077, and MG9082.

These chips will receive 1 or 2 SGPIO streams and drive LEDs accordingly; the latest chip from AMI, the MG9077, can be configured by pull-up and pull-down resistors to adopt to 16 different configurations of SGPIO buses and drive the LEDs accordingly. Since the availability of these chips from AMI, major OEMs including NEC, Hitachi, Supermicro, IBM, Sun Microsystems, and others are using them on their back-planes to receive the SGPIO streams from a variety of HBA vendors and on-board controller chips to consistently drive LEDs with a pre-determined blinking pattern.

External links

- SFF-8485 Specification for Serial GPIO (SGPIO) Bus

- SFF Documents (Documents & Specifications)